شروع کار با بردهای اف پی جی ای MOJO

FPGA یا Field-Programmable Gate Array یک مدار مجتمع است که دارای بلوک های منطقی قابل پیکربندی (CLBs) و سایر ویژگی هایی است که توسط کاربر قابل برنامه ریزی و بازبرنامه ریزی است. عبارت “قابل برنامه ریزی در میدان” نشان می دهد که توانایی های FPGA قابل تنظیم هستند و توسط سازنده مانند سایر IC ها سخت افزاری نمی شوند .

Xilinx یک شرکت معروف در زمینه تولید FPGA ها است. این شرکت انواع مختلف FPGA ها را در خانواده های Artix®، Kintex® و Virtex® ارائه می دهد . Spartan 6 نیز یک FPGA از شرکت Xilinx است که ویژگی های اتصال پیشروی صنعتی مانند نسبت بالای منطق به پین (high logic-to-pin ratios)، بسته بندی فرم فاکتور کوچک (small form-factor packaging)، پردازنده نرم MicroBlaze و تعداد متنوعی از پروتکل های I/O پشتیبانی شده (diverse number of supported I/O protocols) را ارائه می دهد. این دستگاه برای طیف گسترده ای از برنامه های پیشرفته پل در مصرف کننده، سرگرمی خودرو و اتوماسیون صنعتی مناسب است .

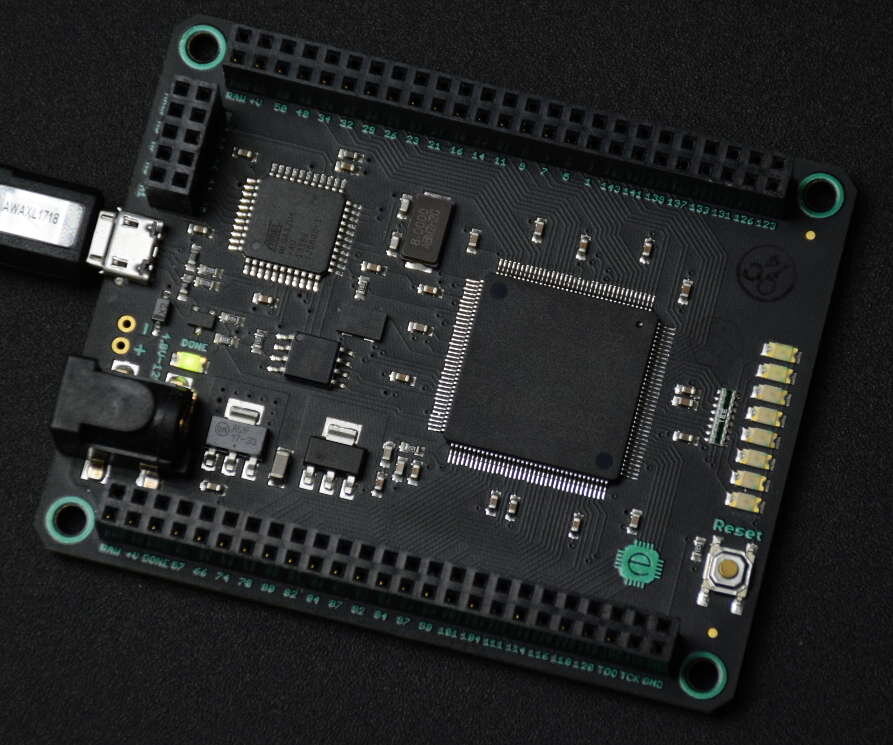

برد اف پی جی ای MOJO

برد MOJO یک برد FPGA است که توسط شرکت Embedded Micro (که اکنون Alchitry نامیده می شود) طراحی شده است. هدف این برد این است که شما را با FPGA به آسان ترین شکل ممکن به راه اندازید. برای همراهی با برد توسعه، مجموعه ای از آموزش ها وجود دارد تا به شما کمک کند تا شروع کنید و دانش خود را در زمینه طراحی دیجیتال گسترش دهید.

برد MOJO v3 با استفاده از Spartan 6 و یک میکروکنترلر عملکرد بالای ATmega32U4 طراحی شده است و قدرت پردازش بالایی دارد. میکروکنترلر ATmega32U4 دارای یک بوت لودر USB (DFU) است که به شما اجازه می دهد نسخه های جدید firmware را بدون نیاز به یک برنامه نویس نصب کنید. هنگامی که برد تغذیه می شود، ATmega32U4 FPGA را از حافظه فلش پیکربندی می کند. پس از پیکربندی موفق FPGA، FPGA شما شروع به صحبت با میکروکنترلر می کند و به شما دسترسی به پورت سریال و ورودی های آنالوگ را می دهد.

- Spartan 6 XC6SLX9 FPGA

- 84 پین دیجیتال IO

- 8 ورودی آنالوگ

- 8 LED های هدفمند

- 1 دکمه ریست

- 1 LED برای نشان دادن زمانی که FPGA به درستی پیکربندی شده است

- تنظیم کننده ولتاژ در برد که می تواند 4.8V تا 12V را مدیریت کند

- یک میکروکنترلر (ATmega32U4) برای پیکربندی FPGA، ارتباطات USB و خواندن پین های آنالوگ استفاده می شود

- بوت لودر سازگار با آردوینو که به شما اجازه می دهد به راحتی میکروکنترلر را برنامه ریزی کنید

- حافظه فلش در برد برای ذخیره فایل پیکربندی FPGA

- نسخه V3 از MOJO دارای یک پورت USB قوی تر از V2، تغییرات جزئی زیبایی شناسی و یک میکروکنترلر ارتقا یافته با حافظه اضافی برای اضافه کردن کد خود است.

ساخت پروژه و پروگرم کردن آن برروی برد MOJO در محیط Alchitry labs

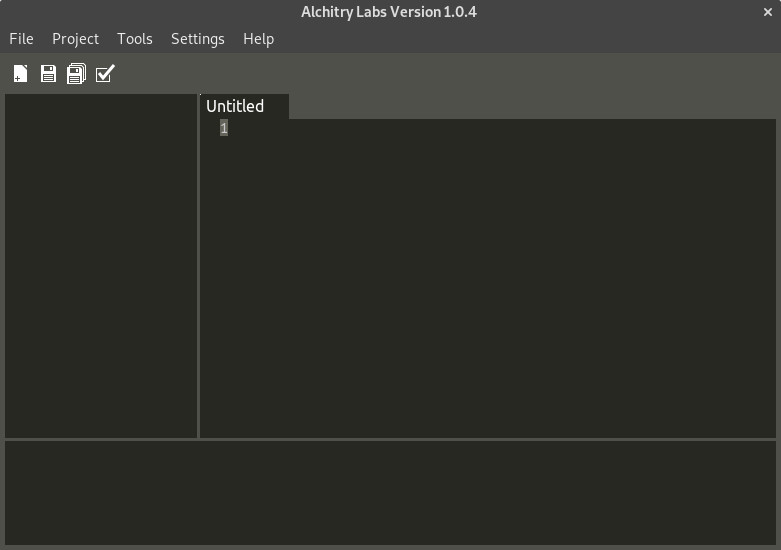

ایجاد یک پروژه جدید Alchitry Labs را اجرا کنید. پس از کلیک بر روی صفحه خوش آمدید، شما باید صفحه زیر را مشاهده کنید.

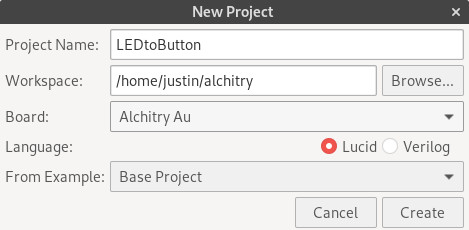

روی File->New Project کلیک کنید. در پنجره ای که باز می شود، نام پروژه LEDtoButton را وارد کنید. می توانید workspace پیش فرض را انتخاب کنید یا برای یک workspace دیگر جستجو کنید. این جایی است که تمام پروژه های شما ذخیره می شوند. از منوی کشویی برای انتخاب بردی که استفاده می کنید استفاده کنید.

زبان را روی Lucid قرار دهید و From Example را روی Base Project قرار دهید. این یک پروژه بدون استفاده را به عنوان نقطه شروع کپی می کند. حالا باید چیزی شبیه به این باشد. توجه داشته باشید که workspace شما متفاوت خواهد بود.

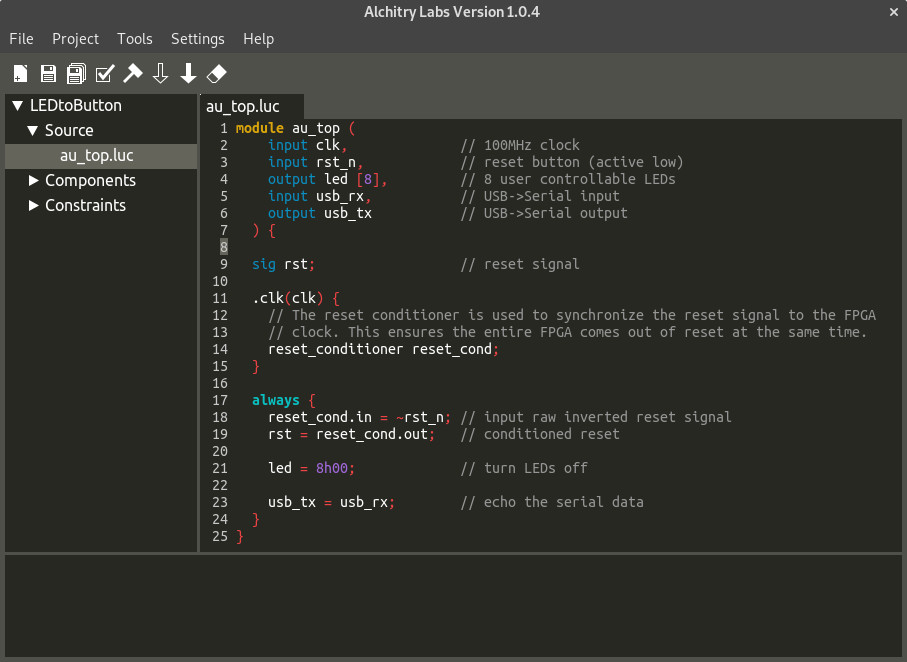

برای ایجاد پروژه خود روی Create کلیک کنید. در پنجره اصلی، درخت سمت چپ را باز کنید تا فایل top در داخل Source را پیدا کنید. این نام board_top.luc دارد. روی آن دوبار کلیک کنید تا آن را در ویرایشگر باز کنید.

فایل top شامل تمام ورودی ها و خروجی های خارجی طرح شما است. پروژه های آینده شما ممکن است از چندین ماژول ساخته شده باشد، اما همگی باید به عنوان زیر ماژول به این ماژول top باشند. این مورد در یک آموزش بعدتر بیشتر پوشش داده خواهد شد. در حال حاضر، ما تمام ویرایش های خود را در این فایل اعمال م

بیلد کردن پروژه و ایجاد بیت استریم

ساخت پروژه شما برای ساخت پروژه خود، روی آیکون چکش کوچک در نوار ابزار کلیک کنید. ممکن است ابتدا باید مشخص کنید که کجا نصب کننده را نصب کرده اید.

برای Au، از Settings->Vivado Location … استفاده کنید و آن را به پوشه Xilinx/Vivado/YEAR.MONTH اشاره کنید.

برای Cu، از Settings->iCEcube2 Location … استفاده کنید و آن را به پوشه lscc/iCEcube2 اشاره کنید. همچنین باید از Settings->iCEcube2 License Location … برای اشاره به فایل مجوزی که هنگام نصب iCEcube2 دانلود کرده اید استفاده کنید.

برای Mojo، از Settings->ISE Location … استفاده کنید و آن را به پوشه Xilinx/14.7 اشاره کنید.

پس از تنظیم، شما باید قادر باشید پروژه خود را بسازید.

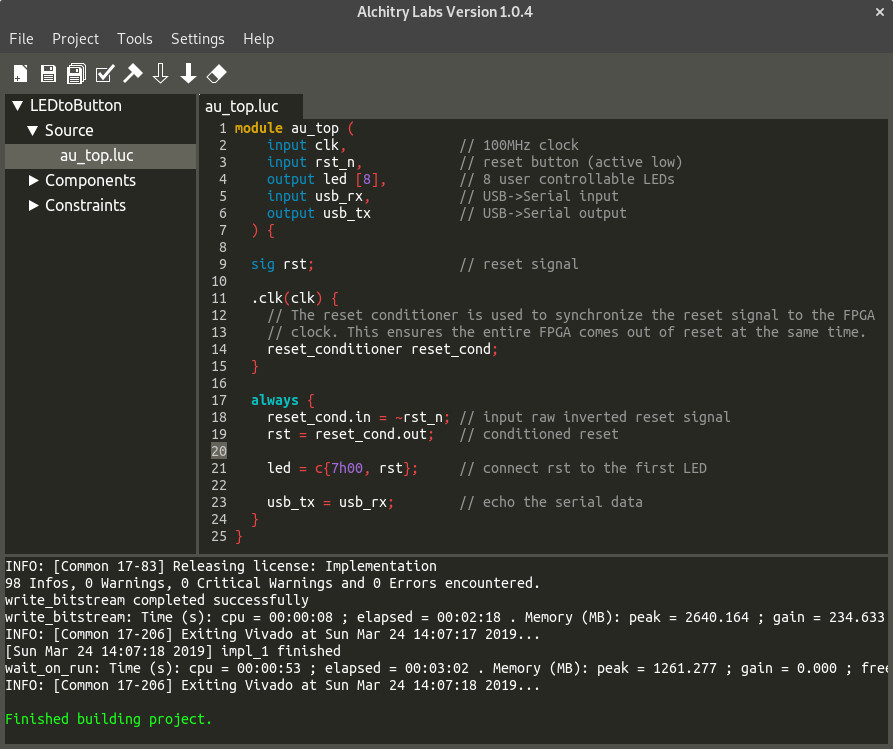

همانطور که پروژه در حال ساخت است، شما باید متن زیادی را ببینید. فقط منتظر باشید تا ساخت آن تمام شود. باید چیزی شبیه به این باشد.

خط مهم در اینجا جایی است که می گوید پروژه ساخته شده تمام شده است. این بدان معنی است که IDE قادر بود پس از آن یک فایل .bin را پیدا کند. اگر هرگز پیام قرمزی دریافت کنید که به شما می گوید فایل bin پیدا نشد، باید در پیام های ساخت بالا بروید تا خطایی را که باعث شکست آن شده است پیدا کنید.

پروگرم کردن برنامه برروی برد های MOJO

بارگذاری پروژه شما با ساخت پروژه خود، اگر هنوز این کار را نکرده اید، برد خود را به رایانه خود وصل کنید.

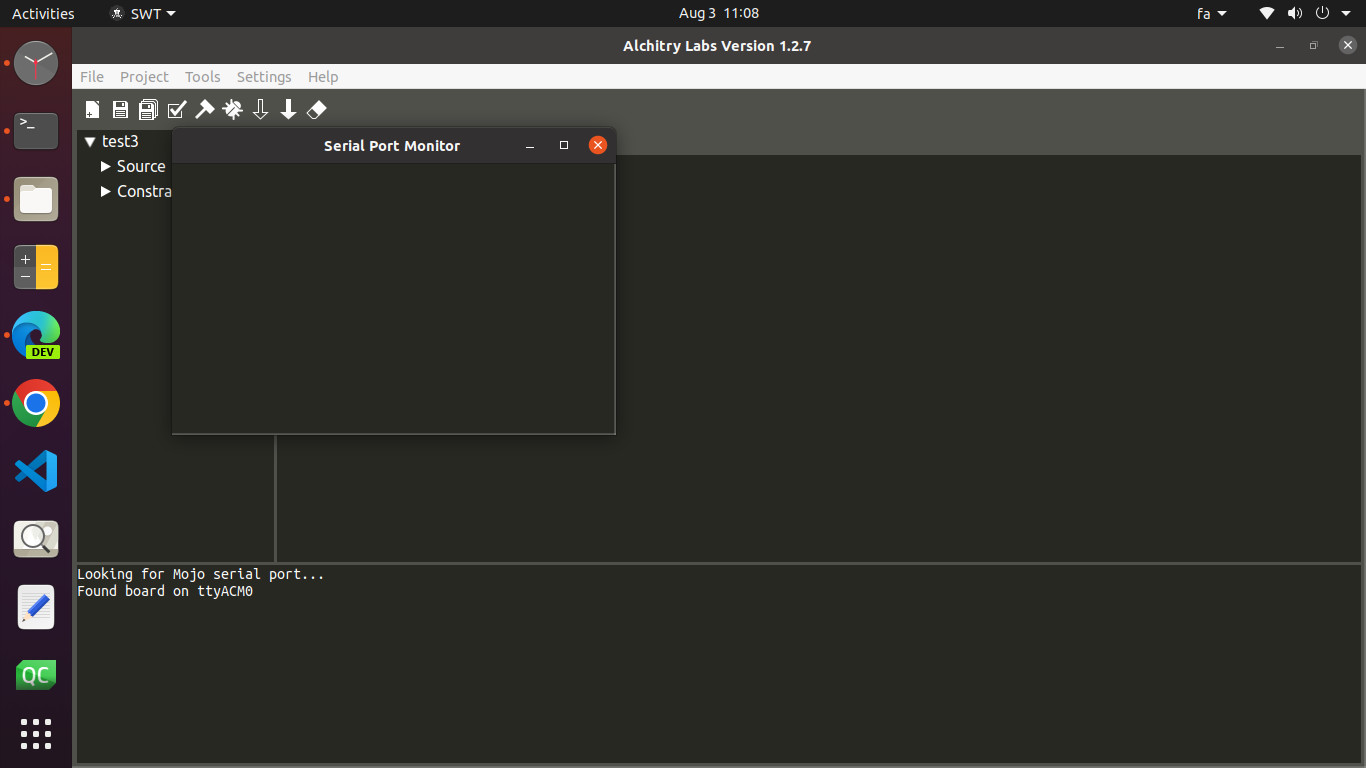

اگر از Mojo استفاده می کنید، به Settings->Serial Port … بروید و پورت سریالی را که Mojo به آن متصل است انتخاب کنید.

بردهای Alchitry به صورت خودکار شناسایی می شوند.

وقت آن است که پروژه خود را روی برد بارگذاری کنید. شما دو گزینه دارید. اولین گزینه، پیکان توخالی است، این پیکربندی برنامه شما را مستقیماً در حافظه RAM FPGA می نویسد. دومین گزینه، پیکان جامد است، این پیکربندی شما را به حافظه FLASH در برد پروگرم می کند. حالت اول با خاموش شدن برد پاک می شود اما حالت دوم همچنان پس از خاموش شدن برد باقی ماند.

حالا به برد خود نگاه کنید. شما باید LED DONE روشن را ببینید. این بدان معنی است که پیکربندی با موفقیت به FPGA بارگذاری شده است.

هنگامی که نرم افزار بتواند برد را پیدا کند مطابق شکل زیر پیغام موفقیت آمیز بودن پیدا شدن برد در قسمت لاگ چاپ خواهد کرد.

مثال یک : نمونه کد وریلاگ روشن شدن چند ال ای دی در برد Mojo – فایل lucid

دانلود فایل پروژه نمونه Mojo با زبان Lucid

مثال دو : نمونه کد وریلاگ روشن شدن چند ال ای دی در برد Mojo – فایل وریلاگ

دانلود فایل پروژه نمونه Mojo با Verilog

//فایل mojo_top

module mojo_top(

// 50MHz clock input

input clk,

// Input from reset button (active low)

input rst_n,

// cclk input from AVR, high when AVR is ready

input cclk,

// Outputs to the 8 onboard LEDs

output[7:0]led,

// AVR SPI connections

output spi_miso,

input spi_ss,

input spi_mosi,

input spi_sck,

// AVR ADC channel select

output [3:0] spi_channel,

// Serial connections

input avr_tx, // AVR Tx => FPGA Rx

output avr_rx, // AVR Rx => FPGA Tx

input avr_rx_busy // AVR Rx buffer full

);

wire rst = ~rst_n; // make reset active high

// these signals should be high-z when not used

assign spi_miso = 1'bz;

assign avr_rx = 1'bz;

assign spi_channel = 4'bzzzz;

assign led = 8'b1111000;

endmoduleفایل ucf یا constraints file

CONFIG VCCAUX=3.3;

NET "clk" TNM_NET = clk;

TIMESPEC TS_clk = PERIOD "clk" 50 MHz HIGH 50%;

NET "clk" LOC = P56 | IOSTANDARD = LVTTL;

NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL;

NET "cclk" LOC = P70 | IOSTANDARD = LVTTL;

NET "led<0>" LOC = P134 | IOSTANDARD = LVTTL;

NET "led<1>" LOC = P133 | IOSTANDARD = LVTTL;

NET "led<2>" LOC = P132 | IOSTANDARD = LVTTL;

NET "led<3>" LOC = P131 | IOSTANDARD = LVTTL;

NET "led<4>" LOC = P127 | IOSTANDARD = LVTTL;

NET "led<5>" LOC = P126 | IOSTANDARD = LVTTL;

NET "led<6>" LOC = P124 | IOSTANDARD = LVTTL;

NET "led<7>" LOC = P123 | IOSTANDARD = LVTTL;

NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL;

NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL;

NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL;

NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL;

NET "spi_channel<0>" LOC = P46 | IOSTANDARD = LVTTL;

NET "spi_channel<1>" LOC = P61 | IOSTANDARD = LVTTL;

NET "spi_channel<2>" LOC = P62 | IOSTANDARD = LVTTL;

NET "spi_channel<3>" LOC = P65 | IOSTANDARD = LVTTL;

NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL;

NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL;

NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL;منابع

https://alchitry.com/your-first-fpga-project-mojo

دیدگاهتان را بنویسید